CMOS LSI

LC82101

# SANYO

# Preliminary

# Overview

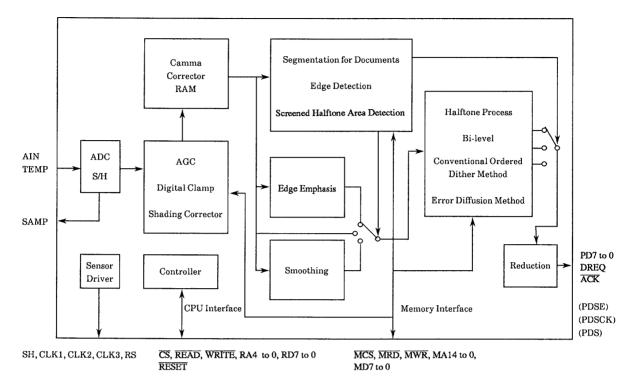

The LC82101 converts an analog image signal from a CCD or contact sensor to high-quality binary image data. The LC82101 uses an internal 8-bit A/D converter for A/D conversion, and in addition to the orthodox dithering technique, also supports an error diffusion technique that allows an even higher quality image to be acquired. These techniques apply to the whole range of processing supported by the LC82101, including full-pixel distortion correction, gamma conversion for arbitrary gamma curves, image compression processing, two-dimensional filtering, halftone processing, and image separation processing to separate documents into text, photograph, and halftone regions. Thus this LSI implements the image processing required by FAX, copier, and OCR systems.

# **Features**

• Number of pixels processed

2048 pixels/line (64 KB memory, white correction only) 4096 pixels/line (256 KB memory, both white and black correction)

8192 pixels/line (256 KB memory, white correction only)

- Processing speed 500 ns/pixel maximum (The processing time for 1 pixel is 16/SYSCLK.)

- Supports medium speed products with a single external memory chip

100 ns access time memory allows 800 ns/pixel processing, and 60 ns access time memory allows 500 ns/pixel processing.

- AGC (The A/D converter high-level reference voltage is varied from 1.2 to 4.2 V in 0.2 V steps.)

- Built-in 8-bit A/D converter (includes a sensor signal delay adjustment function)

- Sensor drive circuit (supports CCD and all CIS types)

- Digital clamp (single-point clamp, even/odd clamp)

- Distortion correction (white correction, black correction, full-pixel correction)

- Gamma correction (supports user-defined curves)

- Image area separation (text, photographs, halftone)

- Simple binary-conversion processing (fixed threshold level, density-adaptive threshold level)

Image Processing Circuit for FAX, Copier, and OCR Products

• Halftone processing Structural dithering (64 levels), settable dithering threshold level

Error diffusion technique (64 levels)

- Image reduction (thinning, fine black line retaining, fine white line retaining)

- Single-voltage 5 V supply and low power due to CMOS process fabrication

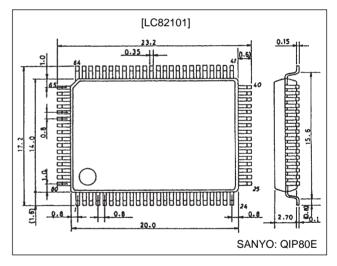

# **Package Dimensions**

unit: mm

## 3174-QFP80E

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

#### **Block Diagram**

#### **Pin Functions**

Type: I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: No connection

| Pin No. | Symbol           | I/O | Function                                                                         |

|---------|------------------|-----|----------------------------------------------------------------------------------|

| 1       | DREQ             | 0   | DMA data request signal output                                                   |

| 2       | ACK              | 1   | DMA acknowledge signal input                                                     |

| 3       | PD0              | 0   |                                                                                  |

| 4       | PD1              | 0   | Binary image data parallel data bus                                              |

| 5       | PD2              | 0   | The data order is set by the MSBF register.                                      |

| 6       | PD3              | 0   |                                                                                  |

| 7       | PD4              | 0   |                                                                                  |

| 8       | PD5/SDE          | 0   | Pin 8 can be switched to function as the serial data output valid period signal. |

| 9       | PD6/SDCK         | 0   | Pin 9 can be switched to function as the serial data transfer clock.             |

| 10      | PD7/SD           | 0   | Pin 10 can be switched to function as the serial data output.                    |

| 11      | MD0              | В   | External memory data bus                                                         |

| 12      | DV <sub>DD</sub> | Р   | Digital system power supply                                                      |

| 13      | DGND             | Р   | Digital system ground                                                            |

| 14      | MD1              | В   |                                                                                  |

| 15      | MD2              | В   |                                                                                  |

| 16      | MD3              | В   |                                                                                  |

| 17      | MD4              | В   | External memory data bus<br>MD7 is the MSB and MD0 is the LSB.                   |

| 18      | MD5              | В   |                                                                                  |

| 19      | MD6              | В   |                                                                                  |

| 20      | MD7              | В   |                                                                                  |

| 21      | DGND             | Р   | Digital system ground                                                            |

| 22      | MA0              | 0   |                                                                                  |

| 23      | MA1              | 0   |                                                                                  |

| 24      | MA2              | 0   |                                                                                  |

| 25      | MA3              | 0   |                                                                                  |

| 26      | MA4              | 0   | External memory address<br>MA14 is the MSB and MA0 is the LSB.                   |

| 27      | MA5              | 0   |                                                                                  |

| 28      | MA6              | 0   |                                                                                  |

| 29      | MA7              | 0   |                                                                                  |

| 30      | MA8              | 0   |                                                                                  |

# LC82101

Continued from preceding page.

Type: I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: No connection

| Pin No. | Symbol           | I/O | Function                                      |  |  |  |

|---------|------------------|-----|-----------------------------------------------|--|--|--|

| 31      | DV <sub>DD</sub> | P   | Digital system power supply                   |  |  |  |

| 32      | DGND             | P   | Digital system ground                         |  |  |  |

| 33      | MA9              | 0   |                                               |  |  |  |

| 34      | MA10             | 0   |                                               |  |  |  |

| 35      | MA11             | 0   | External memory address bus                   |  |  |  |

| 36      | MA12             | 0   | MA14 is the MSB and MA0 is the LSB.           |  |  |  |

| 37      | MA13             | 0   |                                               |  |  |  |

| 38      | MA14             | 0   |                                               |  |  |  |

| 39      | MCS              | 0   | External memory CS signal                     |  |  |  |

| 40      | MRD              | 0   | External memory READ signal                   |  |  |  |

| 41      | MWR              | 0   | External memory WRITE signal                  |  |  |  |

| 41      | DGND             | P   | Digital system ground                         |  |  |  |

| 43      | MTP              | 0   | Motor drive timing signal output              |  |  |  |

| 43      | SH               | 0   |                                               |  |  |  |

| 44      | RS               | 0   |                                               |  |  |  |

|         |                  | 0   |                                               |  |  |  |

| 46      | CLK1             | 0   | Sensor drive signal outputs                   |  |  |  |

| 47      | CLK2             | _   |                                               |  |  |  |

| 48      | CLK3             | 0   | Ormalian de la mariter                        |  |  |  |

| 49      | SAMP             | 0   | Sampling clock monitor                        |  |  |  |

| 50      | CLKIN            |     | System clock input                            |  |  |  |

| 51      | DV <sub>DD</sub> | P   | Digital system power supply                   |  |  |  |

| 52      | DGND             | P   | Digital system ground                         |  |  |  |

| 53      | NC               | NC  |                                               |  |  |  |

| 54      | NC               | NC  |                                               |  |  |  |

| 55      | NC               | NC  |                                               |  |  |  |

| 56      | TEST             |     | Test input (Connect to ground in normal use.) |  |  |  |

| 57      | AGND             | P   | Analog system ground                          |  |  |  |

| 58      | ATAP             | 0   | Analog mid-level connection                   |  |  |  |

| 59      | AIN              |     | Sensor signal input                           |  |  |  |

| 60      | TEMP             |     | Temperature signal input                      |  |  |  |

| 61      | AV <sub>DD</sub> | P   | Analog system power supply                    |  |  |  |

| 62      | RD0              | В   |                                               |  |  |  |

| 63      | RD1              | В   |                                               |  |  |  |

| 64      | RD2              | В   |                                               |  |  |  |

| 65      | RD3              | В   | CPU interface data bus                        |  |  |  |

| 66      | RD4              | В   | RD7 is the MSB and RD0 is the LSB.            |  |  |  |

| 67      | RD5              | В   |                                               |  |  |  |

| 68      | RD6              | В   |                                               |  |  |  |

| 69      | RD7              | В   |                                               |  |  |  |

| 70      | RA0              | I   | CPU interface address bus                     |  |  |  |

| 71      | RA1              | I   | RA4 is the MSB and RA0 is the LSB.            |  |  |  |

| 72      | RA2              | I   |                                               |  |  |  |

| 73      | DV <sub>DD</sub> | Р   | Digital system power supply                   |  |  |  |

| 74      | DGND             | Р   | Digital system ground                         |  |  |  |

| 75      | RA3              | I   | CPU interface address bus                     |  |  |  |

| 76      | RA4              | I   |                                               |  |  |  |

| 77      | CS               | I   | CPU interface CS signal                       |  |  |  |

| 78      | READ             | I   | CPU interface READ signal                     |  |  |  |

| 79      | WRITE            | I   | CPU interface WRITE signal                    |  |  |  |

| 80      | RESET            | I   | System reset                                  |  |  |  |

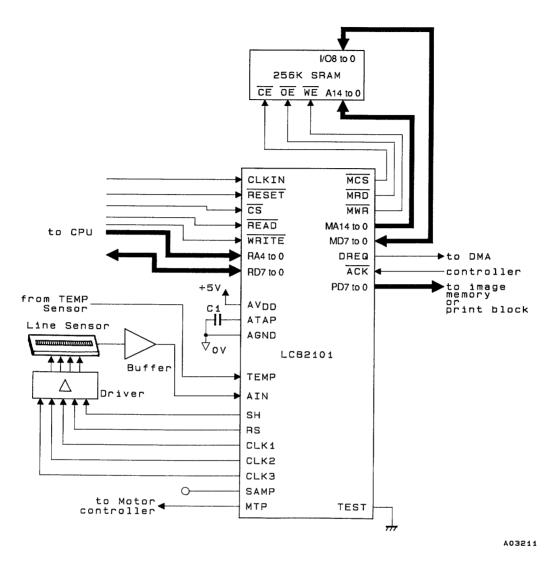

### **Sample Application Circuit**

- 1. C1: Use a 0.01 µF laminated ceramic capacitor.

- 2. Set up the polarity of the image signal from the sensor so that white data is represented by the highest potential and black data by the lowest potential. A level conversion circuit can allow the whole dynamic range of the built-in A/D converter to be used effectively if the maximum output level of the peaks in the image signal from the sensor does not reach 4.2 V.

- 3. When a 64 K SRAM is used as the distortion correction memory, leave MA11 and MA12 unused and connect MA13 and MA14 to the memory A11 and A12 lines.

- 4. Although AGND and DGND are completely isolated internally in this LSI,  $AV_{DD}$  and  $DV_{DD}$  are connected through the substrate. Therefore, the power supply system must be designed so that no potential difference between  $AV_{DD}$  and  $DV_{DD}$  can occur. Also, when power is applied or removed, the time lag between the power supplies must be under 3 ms.

# **Specifications**

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , GND = 0 V

| Parameter                   | Symbol                          | Conditions                   | Ratings                       | Unit |

|-----------------------------|---------------------------------|------------------------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max             |                              | -0.3 to +7.0                  | V    |

| I/O voltages                | V <sub>I</sub> , V <sub>O</sub> |                              | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max                          | Ta ≤ 70°C                    | 450                           | mW   |

| Operating temperature       | Topr                            |                              | -30 to +70                    | °C   |

| Storage temperature         | Tstg                            |                              | -55 to +125                   | °C   |

| Coldering conditions        |                                 | Hand soldering: 3 seconds    | 350                           | °C   |

| Soldering conditions        |                                 | Reflow soldering: 10 seconds | 235                           | °C   |

#### Allowable Operating Conditions at Ta = -30 to $+70^{\circ}C$ , GND = 0 V

| Parameter      | Symbol          | Conditions | min | typ | max             | Unit |

|----------------|-----------------|------------|-----|-----|-----------------|------|

| Supply voltage | V <sub>DD</sub> |            | 4.5 |     | 5.5             | V    |

| Input voltage  | V <sub>IN</sub> |            | 0   |     | V <sub>DD</sub> | V    |

#### DC Characteristics at Ta = -30 to $+70^{\circ}$ C, GND = 0 V, V<sub>DD</sub> = 4.5 to 5.5 V

| Parameter                 | Symbol          | Conditions                               | min  | typ | max  | Unit |

|---------------------------|-----------------|------------------------------------------|------|-----|------|------|

| Input high-level voltage  | VIH             |                                          | 2.2  |     |      | V    |

| Input low-level voltage   | VIL             |                                          |      |     | 0.8  | V    |

| Input leakage current     | ١L              | $V_{IN} = V_{DD}, V_{SS}$                | -25  |     | +25  | μA   |

| Output high-level voltage | V <sub>OH</sub> | I <sub>OH</sub> = 3 mA                   | 2.4  |     |      | V    |

| Output low-level voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3 mA                   |      |     | 0.4  | V    |

| Output leakage current    | ١L              | When in the high-impedance state         | -100 |     | +100 | μA   |

| Current drain             | I <sub>DD</sub> | V <sub>DD</sub> = 5.0 V, SYSCLK = 32 MHz |      | 40  | 60   | mA   |

#### Analog Characteristics

# The minimum signal level in analog input signals must be matched to AGND, and the maximum signal level must not exceed the maximum AGC potential.

| Parameter                                                                            | Symbol | Conditions | min  | typ  | max  | Unit               |  |  |  |

|--------------------------------------------------------------------------------------|--------|------------|------|------|------|--------------------|--|--|--|

| [When AGND = 0 V]                                                                    |        |            |      |      |      |                    |  |  |  |

| Maximum potential                                                                    |        |            | 0.82 | 0.84 | 0.86 | AV <sub>DD</sub> V |  |  |  |

| Minimum potential                                                                    |        |            | 0.22 | 0.24 | 0.26 | AV <sub>DD</sub> V |  |  |  |

| [When AV <sub>DD</sub> = 5.0 V, AGND = 0 V, and the AGC is at the maximum potential] |        |            |      |      |      |                    |  |  |  |

| Resolution                                                                           |        |            |      | 8    |      | bit                |  |  |  |

| Linearity error                                                                      |        |            |      |      | ±1   | LSB                |  |  |  |

| Differential linearity error                                                         |        |            |      |      | ±1   | LSB                |  |  |  |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1995. Specifications and information herein are subject to change without notice.