### **32C408B** 4 Megabit (512K x 8-Bit) SRAM

#### **FEATURES:**

- 512k x 8-bit CMOS architecture

- Rad-Pak® technology hardened against natural space radiation

- Total dose hardness:

- > 100 krad (Si), depending upon space mission

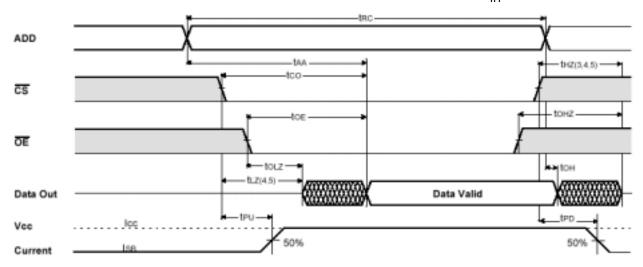

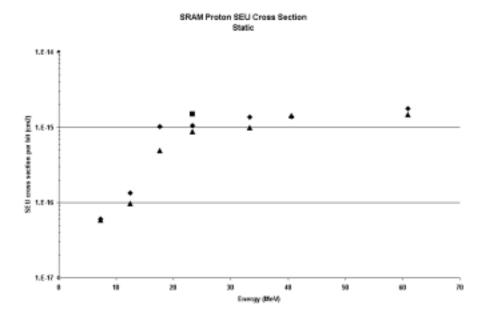

- Single event effect:

- $SEL_{TH}$ :  $\geq$  68 MeV/mg/cm<sup>2</sup>

- SEU<sub>TH</sub>: < 3MeV/mg/cm<sup>2</sup>

- SEU saturated cross section: 6E-9 cm<sup>2</sup>/bit

- Package:

- -36 pin Rad-Pak® flat pack

- Fast propagation time:

- -20, 25, 30 ns maximum access time

- Single 5V <u>+</u> 10% power supply

- · Low power dissipation:

- Standby: 60mA (TTL); 10mA (CMOS)

- Operating: 180 mA (20 ns); 170 mA (25 ns); 160 mA (30 ns)

- TTL compatible inputs and outputs

- Fully static operation

- No clock or refresh required

- Three state outputs

#### **DESCRIPTION:**

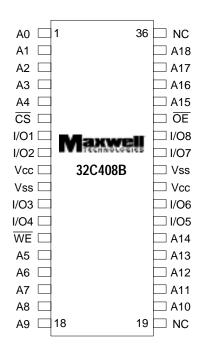

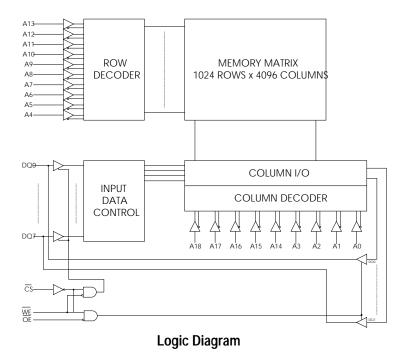

Maxwell Technologies' 32C408B high-speed 4 Megabit SRAM microcircuit features a greater than 100 krad (Si) total dose tolerance, depending upon space mission. Using Rad-Pak® packaging technology, the 32C408B realizes higher density, higher performance and lower power consumption, and is well suited for high-speed system application. Its fully static design eliminates the need for external clocks, while the CMOS circuitry reduces power consumption and provides higher reliability. The 32C408B is equipped with eight common input/output lines, chip select and output enable, allowing for greater system flexibility and eliminating bus contention.

Maxwell Technologies' patented RAD-PAK packaging technology incorporates radiation shielding in the microcircuit package. In a GEO orbit, RAD-PAK can provides true greater than 100 krad (Si) total radiation dose tolerance; dependent upon space mission. The patented radiation-hardened RAD-PAK technology incorporates radiation shielding in the microcircuit package. It eliminates the need for box shielding while providing the required radiation shielding for a lifetime in orbit or a space mission. This product is available with packaging and screening up to Class S.

Table 1. 32C408B Absolute Maximum Ratings

| Parameter                                                     | Symbol                             | Min  | Max                  | Unit |

|---------------------------------------------------------------|------------------------------------|------|----------------------|------|

| Voltage on any pin relative to V <sub>SS</sub>                | V <sub>IN</sub> , V <sub>OUT</sub> | -0.5 | V <sub>CC</sub> +0.5 | V    |

| Voltage on V <sub>CC</sub> supply relative to V <sub>SS</sub> | V <sub>CC</sub>                    | -0.5 | 7.0                  | V    |

| Power Dissipation                                             | $P_{D}$                            |      | 1.0                  | W    |

| Storage Temperature                                           | T <sub>S</sub>                     | -65  | +150                 | °C   |

| Operating Temperature                                         | T <sub>A</sub>                     | -55  | +125                 | °C   |

TABLE 2. 32C408B RECOMMENDED OPERATING CONDITIONS

| Parameter                       | Symbol                | Min  | Max                  | Unit |

|---------------------------------|-----------------------|------|----------------------|------|

| Supply Voltage                  | V <sub>CC</sub>       | 4.5  | 5.5                  | V    |

| Ground                          | $V_{SS}$              | 0    | 0                    | V    |

| Input High Voltage <sup>1</sup> | V <sub>IH</sub>       | 2.2  | V <sub>CC</sub> +0.5 | V    |

| Input Low Voltage <sup>2</sup>  | V <sub>IL</sub>       | -0.5 | 0.8                  | V    |

| Thermal Impedance               | $\Theta_{	extsf{JC}}$ |      | 0.63                 | °C/W |

<sup>1.</sup>  $V_{IH}(max) = V_{CC} + 2.0V$  ac(pulse width  $\leq 10$ ns) for  $I \leq 20$ mA.

### TABLE 3. 32C408B DC ELECTRICAL CHARACTERISTICS

( $V_{CC}$ =5V +/- 10%,  $T_A$  = -55 to +1'25C, Unless Oterwise Specified

| Parameter                             | Condition                                                                                                                                                                                                                              | Symbol           | Subgroups | Min      | Түр | Max               | Unit |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|----------|-----|-------------------|------|

| Input Leakage Current                 | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                                                                                          | I <sub>LI</sub>  | 1, 2, 3   | -2       |     | 2                 | μA   |

| Output Leakage Current                | $\overline{\text{CS}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{OE}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{WE}} = \text{V}_{\text{IL}},$ $\text{V}_{\text{OUT}} = \text{V}_{\text{SS}} \text{ to V}_{\text{CC}}$ | I <sub>LO</sub>  | 1, 2, 3   | -2       |     | 2                 | μА   |

| Output Low Voltage                    | I <sub>OL</sub> = 8mA                                                                                                                                                                                                                  | V <sub>OL</sub>  | 1, 2, 3   |          |     | 0.4               | V    |

| Output High Voltage                   | I <sub>OH</sub> = -4mA                                                                                                                                                                                                                 | V <sub>OH</sub>  | 1, 2, 3   | 2.4      |     |                   | V    |

| Average Operating Current -20 -25 -30 | Min cycle, 100% Duty, $\overline{CS}=V_{IL}$ , $I_{OUT}=0$ mA, $V_{IN}=V_{IH}$ or $V_{IL}$                                                                                                                                             | I <sub>cc</sub>  | 1, 2, 3   | <br><br> |     | 180<br>170<br>160 | mA   |

| Standby Power Supply                  | CS = V <sub>IH</sub>                                                                                                                                                                                                                   | I <sub>SB</sub>  | 1, 2, 3   |          |     | 60                | mA   |

| Current                               |                                                                                                                                                                                                                                        | I <sub>SB1</sub> | 1, 2, 3   |          |     | 10                |      |

| Input Capacitance <sup>1</sup>        | $V_{IN} = 0V$ , $f = 1MHz$ , $T_A = 25 °C$ .                                                                                                                                                                                           | C <sub>IN</sub>  | 1, 2, 3   |          |     | 7                 | pF   |

| Output Capacitance <sup>1</sup>       | V <sub>I/O</sub> = 0V                                                                                                                                                                                                                  | C <sub>I/O</sub> | 1, 2, 3   |          |     | 8                 | pF   |

<sup>1.</sup> Guaranteed by Design

<sup>2.</sup>  $V_{IL}$  (min) = -2.0V ac(pulse width  $\leq$  10ns) for I  $\leq$  20mA.

## 32C408B

# 4 Megabit (512K x 8-Bit) SRAM

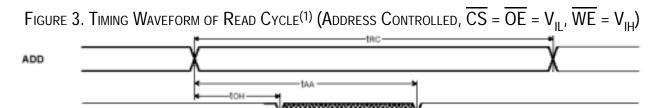

#### TABLE 4. 32C408B AC CHARACTERISTICS FOR READ CYCLE

( $V_{CC}$ =5V +/- 10%,  $T_A$  = -55 to +1'25C, Unless Oterwise Specified

| Parameter                            | Symbol           | Subgroups | Min | Түр | Max | Unit |

|--------------------------------------|------------------|-----------|-----|-----|-----|------|

| Read Cycle Time                      | t <sub>RC</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                                  |                  |           | 20  |     |     |      |

| -25                                  |                  |           | 25  |     |     |      |

| -30                                  |                  |           | 30  |     |     |      |

| Address Access Time                  | t <sub>AA</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                                  |                  |           |     |     | 20  |      |

| -25                                  |                  |           |     |     | 25  |      |

| -30                                  |                  |           |     |     | 30  |      |

| Chip Select Access Time              | t <sub>co</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                                  | 00               |           |     |     | 20  |      |

| -25                                  |                  |           |     |     | 25  |      |

| -30                                  |                  |           |     |     | 30  |      |

| Output Enable to Output Valid        | t <sub>OE</sub>  | 9, 10, 11 |     |     |     |      |

| -20                                  | ,OF              | 7, 10, 11 |     |     | 10  | ns   |

| -25                                  |                  |           |     |     | 12  |      |

| -30                                  |                  |           |     |     | 14  |      |

| Chip Select to Output in Low-Z       | +                | 9, 10, 11 |     |     |     | ns   |

| -20                                  | t <sub>LZ</sub>  | 7, 10, 11 |     | 3   |     | 113  |

| -25                                  |                  |           |     | 3   |     |      |

| -30                                  |                  |           |     | 3   |     |      |

|                                      | 1                | 0 10 11   |     | 3   |     |      |

| Output Enable to Output in Low-Z -20 | t <sub>OLZ</sub> | 9, 10, 11 |     | 0   |     | ns   |

| -20<br>-25                           |                  |           |     | 0   |     |      |

| -25<br>-30                           |                  |           |     | 0   |     |      |

|                                      |                  | 0.40.44   |     | U   |     |      |

| Chip Deselect to Output in High-Z    | t <sub>HZ</sub>  | 9, 10, 11 |     | _   |     | ns   |

| -20                                  |                  |           |     | 5   |     |      |

| -25                                  |                  |           |     | 6   |     |      |

| -30                                  |                  |           |     | 8   |     |      |

| Output Disable to Output in High-Z   | t <sub>OHZ</sub> | 9, 10, 11 |     |     |     | ns   |

| -20                                  |                  |           |     | 5   |     |      |

| -25                                  |                  |           |     | 6   |     |      |

| -30                                  |                  |           |     | 8   |     |      |

| Output Hold from Address Change      | t <sub>OH</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                                  |                  |           | 3   |     |     |      |

| -25                                  |                  |           | 5   |     |     |      |

| -30                                  |                  |           | 5   |     |     |      |

| Chip Select to Power Up Time         | t <sub>PU</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                                  | FU               |           |     | 0   |     |      |

| -25                                  |                  |           |     | 0   |     |      |

| -30                                  |                  |           |     | 0   |     |      |

| Chip Select to Power Down Time       | t <sub>PD</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                                  | የሀ               | 7, 10, 11 |     | 10  |     | 5    |

| -25                                  |                  |           |     | 15  |     |      |

| -30                                  |                  |           |     | 20  |     |      |

|                                      |                  |           |     | 20  |     |      |

Table 5. 32408B Functional Description <sup>1</sup>

| CS | WE | ŌĒ | Mode           | I/O Pin          | SUPPLY CURRENT                     |

|----|----|----|----------------|------------------|------------------------------------|

| Н  | Х  | Х  | Not Select     | High-Z           | I <sub>SB</sub> , I <sub>SB1</sub> |

| L  | Н  | Н  | Output Disable | High-Z           | I <sub>cc</sub>                    |

| L  | Н  | L  | Read           | D <sub>OUT</sub> | I <sub>cc</sub>                    |

| L  | L  | Х  | Write          | D <sub>IN</sub>  | I <sub>cc</sub>                    |

<sup>1.</sup> X = don't care.

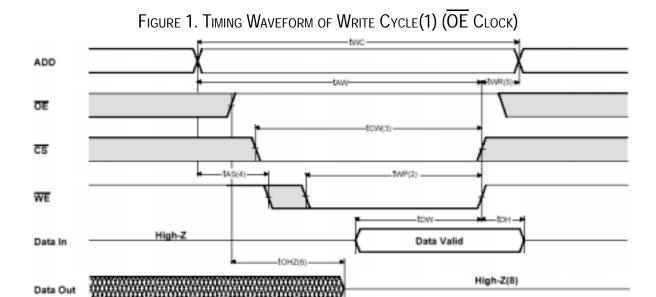

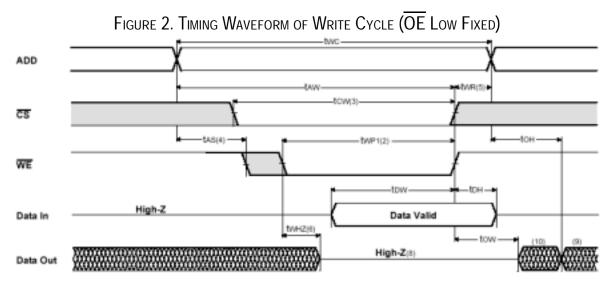

#### TABLE 6. 32C408B AC CHARACTERISTICS FOR WRITE CYCLE

( $V_{CC}$ =5V +/- 10%,  $T_A$  = -55 to +1'25C, Unless Oterwise Specified

| Parameter                     | Symbol           | Subgroups | Min | Түр | Max | Unit |

|-------------------------------|------------------|-----------|-----|-----|-----|------|

| Write Cycle Time              | t <sub>wc</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                           |                  |           | 20  |     |     |      |

| -25                           |                  |           | 25  |     |     |      |

| -30                           |                  |           | 30  |     |     |      |

| Chip Select to End of Write   | t <sub>CW</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                           | <b></b>          |           | 14  |     |     |      |

| -25                           |                  |           | 15  |     |     |      |

| -30                           |                  |           | 17  |     |     |      |

| Address Setup Time            | t <sub>AS</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                           | 7.0              |           | 0   |     |     |      |

| -25                           |                  |           | 0   |     |     |      |

| -30                           |                  |           | 0   |     |     |      |

| Address Valid to End of Write | t <sub>AW</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                           |                  |           | 14  |     |     |      |

| -25                           |                  |           | 15  |     |     |      |

| -30                           |                  |           | 17  |     |     |      |

| Write Pulse Width (OE High)   | t <sub>WP</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                           |                  |           | 14  |     |     |      |

| -25                           |                  |           | 15  |     |     |      |

| -30                           |                  |           | 17  |     |     |      |

| Write Recovery Time           | t <sub>WR</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                           |                  |           | 0   |     |     |      |

| -25                           |                  |           | 0   |     |     |      |

| -30                           |                  |           | 0   |     |     |      |

| Write to Output in High-Z     | t <sub>WHZ</sub> | 9, 10, 11 |     |     |     | ns   |

| -20                           | 2                |           |     | 5   |     |      |

| -25                           |                  |           |     | 5   |     |      |

| -30                           |                  |           |     | 6   |     |      |

## 4 Megabit (512K x 8-Bit) SRAM

TABLE 6. 32C408B AC CHARACTERISTICS FOR WRITE CYCLE

( $V_{\text{CC}}$ =5V +/- 10%,  $T_{A}$  = -55 to +1'25C, Unless Oterwise Specified

| PARAMETER                   | Symbol           | Subgroups | Min | Түр | Max | Unit |

|-----------------------------|------------------|-----------|-----|-----|-----|------|

| Write Pulse Width(OE Low)   | t <sub>WP1</sub> | 9, 10, 11 |     |     |     | ns   |

| -20                         |                  |           |     | 20  |     |      |

| -25                         |                  |           |     | 25  |     |      |

| -30                         |                  |           |     | 30  |     |      |

| Data to Write Time Overlap  | t <sub>DW</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                         |                  |           | 9   |     |     |      |

| -25                         |                  |           | 10  |     |     |      |

| -30                         |                  |           | 11  |     |     |      |

| End Write to Output Low-Z 1 | tOW              | 9, 10, 11 |     |     |     | ns   |

| -20                         |                  |           |     | 6   |     |      |

| -25                         |                  |           |     | 7   |     |      |

| -30                         |                  |           |     | 8   |     |      |

| Data Hold from Write Time   | t <sub>DH</sub>  | 9, 10, 11 |     |     |     | ns   |

| -20                         | ]                |           | 0   |     |     |      |

| -25                         |                  |           | 0   |     |     |      |

| -30                         |                  |           | 0   | 1   | -   |      |

- 1. All write cycle timing is referenced from the last valid address to the first transition address.

- 2. A write occurs during the overlap of a low  $\overline{\text{CS}}$  and a low  $\overline{\text{WE}}$ . A write begins at the latest transition among  $\overline{\text{CS}}$  going low and  $\overline{\text{WE}}$  going low: A write ends at the earliest transition among  $\overline{\text{CS}}$  going high or  $\overline{\text{WE}}$  going high.  $t_{\text{WP}}$  is measured from beginning of write to end of write.

- 3.  $t_{CW}$  is measured from the later of  $\overline{CS}$  going low to end of write.

- 4.  $t_{AS}$  is measured from the address valid to the beginning of write.

Previous Data Valid

- 5.  $t_{WR}$  is measured from the end of write to the address change. TWR applied in case a write ends as  $\overline{CS}$  or  $\overline{WE}$  going high.

- 6. If  $\overline{OE}$ ,  $\overline{CS}$  and  $\overline{WE}$  are in the Read Mode during this period, the I/O pins are in the output low-Z state. Inputs of opposite phase of the output must not be applied because bus contention can occur.

- 7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

- 8. IC  $\overline{\text{CS}}$  goes low simultaneously with  $\overline{\text{WE}}$  going low or after  $\overline{\text{WE}}$  going low, the outputs remain high impedance state.

- 9. D<sub>OUT</sub> is the read data of the new address.

Data Out

10. When CS is low: I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be applied.

Data Valid

FIGURE 4. TIMING WAVEFORM OF READ CYCLE<sup>(2)</sup> ( $\overline{WE} = V_{IH}$ )

- 1. WE is high for read cycle.

- 2. All read cycle timing is referenced from the last valid address to the first transition address.

- 3.  $t_{HZ}$  and  $t_{OHZ}$  are defined as the time at which the outputs achieve the open circuit condition and are not referenced to  $V_{OH}$  or  $V_{OH}$  levels.

- 4. At any given temperature and voltage condition,  $t_{HZ(max)}$  is less than  $t_{LZ(min)}$  both for a given device and from device to device.

- 5. Transition is measured +200mV from steady state voltage with Load(B). This parameter is sampled and not 100% tested.

- 6. Device is continuously selected with  $\overline{CS} = V_{II}$ .

- 7. Address valid prior to coincident with  $\overline{CS}$  transition low.

- 8. For common I/O applications, minimization or elimination of bus contention is necessary during read and write cycle.

FIGURE 5. SRAM HEAVY ION CROSS SECTION

05.02.02 Rev 7

All data sheets are subject to change without notice

FIGURE 6. SRAM PROTON SEU CROSS SECTION STATIC

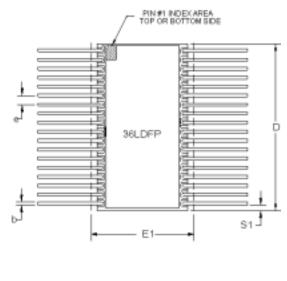

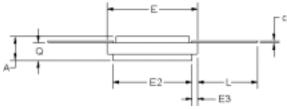

36 PIN FLAT RAD-PAK® PACKAGE

| Symbol | DIMENSION |       |       |  |  |  |

|--------|-----------|-------|-------|--|--|--|

|        | Min       | Nом   | Max   |  |  |  |

| A      | 0.122     | 0.135 | 0.148 |  |  |  |

| b      | 0.015     | 0.017 | 0.019 |  |  |  |

| С      | 0.008     | 0.010 | 0.012 |  |  |  |

| D      |           | 0.930 | 0.940 |  |  |  |

| E      | 0.638     | 0.645 | 0.652 |  |  |  |

| E1     |           |       | 0.690 |  |  |  |

| E2     | 0.560     | 0.565 |       |  |  |  |

| E3     | 0.005     | 0.040 |       |  |  |  |

| е      | 0.050 BSC |       |       |  |  |  |

| L      | 0.390     | 0.400 | 0.410 |  |  |  |

| Q      | 0.088     | 0.098 | 0.108 |  |  |  |

| S1     | 0.005     | 0.032 |       |  |  |  |

| N      | 36        |       |       |  |  |  |

F36-01

Note: All dimensions in inches

32C408B

### 4 Megabit (512K x 8-Bit) SRAM

Important Notice:

These data sheets are created using the chip manufacturers published specifications. Maxwell Technologies verifies functionality by testing key parameters either by 100% testing, sample testing or characterization.

The specifications presented within these data sheets represent the latest and most accurate information available to date. However, these specifications are subject to change without notice and Maxwell Technologies assumes no responsibility for the use of this information.

Maxwell Technologies' products are not authorized for use as critical components in life support devices or systems without express written approval from Maxwell Technologies.

Any claim against Maxwell Technologies must be made within 90 days from the date of shipment from Maxwell Technologies. Maxwell Technologies' liability shall be limited to replacement of defective parts.

# 4 Megabit (512K x 8-Bit) SRAM

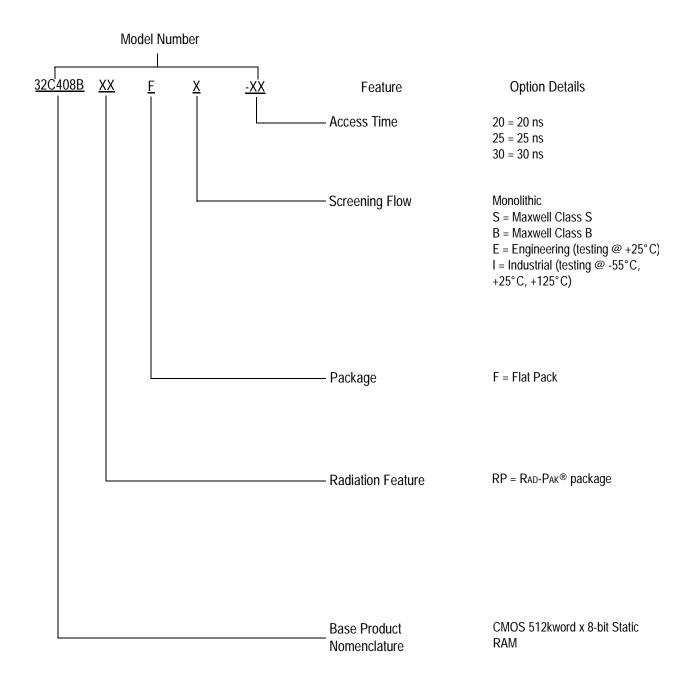

### **Product Ordering Options**