Austin Semiconductor, Inc.

### 128K x 32 EEPROM

Radiation Tolerant EEPROM Memory Array

### AVAILABLE AS MILITARY SPECIFICATIONS

MIL-STD-883

### FEATURES

- Access time of 150ns

- Operation with single  $5V \pm 10\%$  supply

- Power Dissipation: Active: 1.43 W (MAX), Max Speed Operation Standby: 7.7 mW (MAX), Battery Back-up Mode

- On-Chip Latches: Address, Data, CE\, OE\, WE\

- Automatic Byte Write: 10 ms (MAX)

- Automatic Page Write (128 bytes): 10 ms (MAX)

- Data protection circuit on power on/off

- Low power CMOS

- 10<sup>4</sup> Erase/Write cycles (in Page Mode)

- Software data protection

- TTL Compatible Inputs and Outputs

- Data Retention: 10 years

- Ready/Busy\ and Data Polling Signals

- Write protection by RES\ pin

- Radiation Tolerant: Proven total dose 40K to 100K RADS\*

- Operating Temperature Ranges: Military: -55°C to +125°C Industrial: -40°C to +85°C

### OPTIONS MARKI

| MAR | KIN | GS |

|-----|-----|----|

|-----|-----|----|

| No. 703 |

|---------|

|         |

### **GENERAL DESCRIPTION**

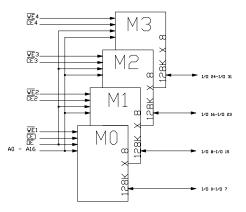

The Austin Semiconductor, Inc. AS8ER128K32 is a 4 Megabit Radiation Tolerant EEPROM Module organized as 128K x 32 bit. User configurable to 256K x16 or 512Kx 8. The module achieves high speed access, low power consumption and high reliability by employing advanced CMOS memory technology.

The military grade product is manufactured in compliance to MIL-STD 883, making the AS8ER128K32 ideally suited for military or space applications.

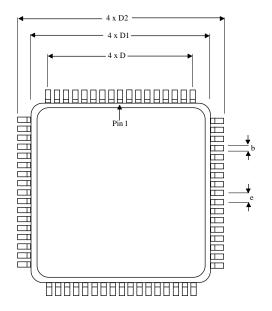

The module is offered as a 68 lead 0.990 inch square ceramic quad flat pack. It has a max. height of 0.200 inch. This package design is targeted for those applications which require low profile SMT Packaging.

\* contact factory for test reports. ASI does not guarantee or warrant these performance levels, but references these third party reports.

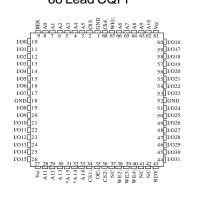

### PIN ASSIGNMENT

(Top View) 68 Lead CQFP

\*Pin #'s 31 and 32, A15 and A14 respectively, are reversed from the AS8E128K32. Correct use of these address lines is required for operation of the SDP mode to work properly.

| PIN NAME        | IAME FUNCTION     |  |

|-----------------|-------------------|--|

| A0 to A16       | Address Input     |  |

| I/O0 to I/O31   | Data Input/Output |  |

| OE\             | Output Enable     |  |

| CE\             | Chip Enable       |  |

| WE\             | Write Enable      |  |

| V <sub>CC</sub> | Power Supply      |  |

| V <sub>SS</sub> | Ground            |  |

| RDY/BUSY\       | Ready Busy        |  |

| RES\            | Reset             |  |

### FUNCTIONAL BLOCK DIAGRAM

For more products and information please visit our web site at www.austinsemiconductor.com

### **TRUTH TABLE**

AS

| MODE          | CE\             | OE\             | WE\             | RES\            | RDY/BUSY\ <sup>1</sup> | I/O         |

|---------------|-----------------|-----------------|-----------------|-----------------|------------------------|-------------|

| Read          | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | $V_{H}^{2}$     | High-Z                 | Dout        |

| Standby       | V <sub>IH</sub> | X <sup>3</sup>  | Х               | Х               | High-Z                 | High-Z      |

| Write         | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>H</sub>  | High-Z to $V_{OL}$     | Din         |

| Deselect      | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>H</sub>  | High-Z                 | High-Z      |

| Wirte Inhibit | Х               | Х               | V <sub>IH</sub> | Х               |                        |             |

|               | Х               | V <sub>IL</sub> | Х               | Х               |                        |             |

| Data\ Polling | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>H</sub>  | V <sub>OL</sub>        | Dout (I/O7) |

| Program Reset | Х               | Х               | Х               | V <sub>IL</sub> | High-Z                 | High-Z      |

**NOTES:** 1. RDY/Busy\ output has only active LOW  $V_{OL}$  and high impedance state. It can not go to HIGH ( $V_{OH}$ ) state.

2.  $V_{CC} - 0.5 \le V_{H} \le V_{CC} + 1.0$ 3. X : DON'T CARE

# Austin Semiconductor, Inc.

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Vcc Supply Relative to Vss

| Vcc0.6V to +7.0V                                                    |

|---------------------------------------------------------------------|

| Operating Temperature Range <sup>(1)</sup> 55°C to +125°C           |

| Storage Temperature Range65°C to +150°C                             |

| Voltage on any Pin Relative to Vss $0.5V$ to $+7.0V$ <sup>(2)</sup> |

| Max Junction Temperature**+150°C                                    |

| Thermal Resistance junction to case $(\theta_{JC})$ :               |

| Package Type Q11.3° C/W                                             |

| Package Type P & PN2.8° C/W                                         |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\*Junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow, and humidity (plastics).

### NOTES:

1) Including electrical characteristics and data retention.

2)  $V_{IN}$  MIN = -3.0V for pulse width < 20ns.

# **ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS** $(-55^{\circ}C \le T_{*} \le 125^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C; Vcc = 5V \pm 10\%)$

| PARAMETER                 | CONDITIONS                                                                                                                   | SYMBOL          | MIN                  | MAX                  | UNITS |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|----------------------|-------|

| Input High Voltage        |                                                                                                                              | V <sub>IH</sub> | 2.2                  | V <sub>CC</sub> +0.3 | V     |

| Input High Voltage (RES\) |                                                                                                                              | V <sub>H</sub>  | V <sub>CC</sub> -0.5 | V <sub>CC</sub> +1.0 | V     |

| Input Low Voltage         |                                                                                                                              | V <sub>IL</sub> | -0.3 <sup>1</sup>    | 0.8                  | V     |

| INPUT LEAKAGE CURRENT     | $OV \leq V_{IN} \leq V_{CC}$                                                                                                 | lu              | -10                  | 10 <sup>2</sup>      | μΑ    |

| OUTPUT LEAKAGE CURRENT    | $\begin{array}{l} \text{Outputs(s) Disabled,} \\ \text{OV} \leq \text{V}_{\text{OUT}} \leq \text{V}_{\text{CC}} \end{array}$ | I <sub>LO</sub> | -10                  | 10                   | μΑ    |

| Output High Voltage       | I <sub>OH</sub> = -0.4mA                                                                                                     | V <sub>OH</sub> | 2.4                  |                      | V     |

| Output Low Voltage        | I <sub>OL</sub> = 2.1mA                                                                                                      | V <sub>OL</sub> |                      | 0.4                  | V     |

| Supply Voltage            |                                                                                                                              | V <sub>CC</sub> | 4.5                  | 5.5                  | V     |

**NOTE:** 1)  $V_{IL}$  (MIN): -1.0V for pulse width < 20ns. 2)  $I_{L1}$  on RES\: 500 $\mu$ A (MAX)

|                       |                                                               |                  | MAX |       |

|-----------------------|---------------------------------------------------------------|------------------|-----|-------|

| PARAMETER             | CONDITIONS                                                    | SYM              | -15 | UNITS |

| Power Supply Current: | lout = 0mA, $V_{CC}$ = 5.5V<br>Cycle = 1 $\mu$ S, Duty = 100% |                  | 80  | mA    |

| Operating             | lout = 0mA, $V_{CC}$ = 5.5V<br>Cycle = MIN, Duty = 100%       | I <sub>cc3</sub> | 260 | ША    |

| Power Supply Current: | $CE = V_{CC,} V_{CC} = 5.5V$                                  | I <sub>CC1</sub> | 1.4 | mA    |

| Standby               | $CE = V_{IH,} V_{CC} = 5.5V$                                  | I <sub>CC2</sub> | 12  | mA    |

Austin Semiconductor, Inc.

### **CAPACITANCE TABLE**<sup>1</sup> ( $V_{IN} = 0V$ , f = 1 MHz, $T_A = 25^{\circ}C$ )

| SYMBOL           | PARAMETER                 | MAX | UNITS |

|------------------|---------------------------|-----|-------|

| C <sub>ADD</sub> | A0 - A16 Capacitance      | 40  | pF    |

| C <sub>OE</sub>  | OE RES RDY Capacitance    | 40  | pF    |

| $C_{WE,}C_{CE}$  | WE\ and CE\ Capacitance   | 12  | pF    |

| C <sub>IO</sub>  | I/O 0- I/O 31 Capacitance | 20  | pF    |

NOTE: 1. This parameter is guaranteed but not tested.

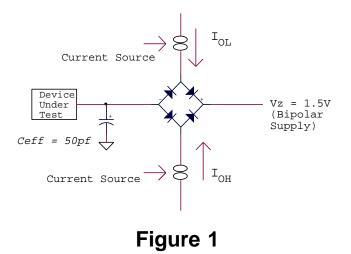

# **AC TEST CHARACTERISTICS**

### **TEST SPECIFICATIONS**

| Input pulse levels            | $\dots V_{ss}$ to 3V |

|-------------------------------|----------------------|

| Input rise and fall times     | 5ns                  |

| Input timing reference levels |                      |

| Output reference levels       |                      |

| Output load                   | See Figure 1         |

### NOTES:

Vz is programmable from -2V to + 7V.  $I_{OL}$  and  $I_{OH}$  programmable from 0 to 16 mA. Vz is typically the midpoint of  $V_{OH}$  and  $V_{OL}$ .  $I_{OL}$  and  $I_{OH}$  are adjusted to simulate a typical resistive load circuit.

### ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(-55^{\circ}C \le T_{A} \le +125^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C; \text{ Vcc} = 5\text{V} \pm 10\%)$

| DESCRIPTION                         | ESCRIPTION TEST CONDITIONS      |                  | 1   | 50  |       |

|-------------------------------------|---------------------------------|------------------|-----|-----|-------|

| DESCRIPTION                         | TEST CONDITIONS                 | SYMBOL           | MIN | MAX | UNITS |

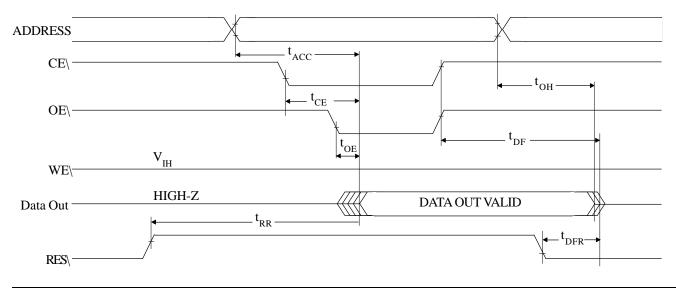

| Address to Output Delay             | $CE = OE = V_{IL}, WE = V_{IH}$ | t <sub>ACC</sub> |     | 150 | ns    |

| CE\ to Output Delay                 | $OE = V_{IL}, WE = V_{IH}$      | t <sub>CE</sub>  |     | 150 | ns    |

| OE\ to Output Delay                 | $OE = V_{IL}, WE = V_{IH}$      | t <sub>OE</sub>  | 10  | 75  | ns    |

| Address to Output Hold              | $CE = OE = V_{IL}, WE = V_{IH}$ | t <sub>OH</sub>  | 0   |     | ns    |

| CE\ or OE\ high to Output Float (1) | $OE = V_{IL}, WE = V_{IH}$      | t <sub>DF</sub>  | 0   | 50  | ns    |

| RES\ low to Output Float (1)        | $CE = OE = V_{IL}, WE = V_{IH}$ | t <sub>DFR</sub> | 0   | 350 | ns    |

| RES\ to Output Delay                | $CE = OE = V_{IL}, WE = V_{IH}$ | t <sub>RR</sub>  | 0   | 450 | ns    |

Austin Semiconductor, Inc.

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC WRITE CHARACTERISTICS (-55°C $\leq T_A \leq +125$ °C; Vcc = 5V $\pm 10$ %)

| SYMBOL           | PARAMETER                                | MIN <sup>(2)</sup> | MAX               | UNITS |

|------------------|------------------------------------------|--------------------|-------------------|-------|

| t <sub>AS</sub>  | Address Setup Time                       | 0                  |                   | ms    |

| t <sub>AH</sub>  | Address Hold Time                        | 150                |                   | ns    |

| t <sub>CS</sub>  | CE\ to Write Setup Time (WE\ controlled) | 0                  |                   | ns    |

| t <sub>CH</sub>  | CE\ Hold Time (WE\ controlled)           | 0                  |                   | ns    |

| t <sub>WS</sub>  | WE\ to Write Setup Time (CE\ controlled) | 0                  |                   | ns    |

| t <sub>WH</sub>  | WE\ to Hold Time (CE\ controlled)        | 0                  |                   | ns    |

| t <sub>OES</sub> | OE\ to Write Setup Time                  | 0                  |                   | ns    |

| t <sub>OEH</sub> | OE\ to Hold Time                         | 0                  |                   | ns    |

| t <sub>DS</sub>  | Data Setup Time                          | 100                |                   | ns    |

| t <sub>DH</sub>  | Data Hold Time                           | 10                 |                   | ns    |

| t <sub>WP</sub>  | WE\ Pulse Width (WE\ controlled)         | 250                |                   | ns    |

| t <sub>CW</sub>  | CE\ Pulse Width (CE\ controlled)         | 250                |                   | ns    |

| t <sub>DL</sub>  | Data Latch Time                          | 300                |                   | ns    |

| t <sub>BLC</sub> | Byte Load Cycle                          | 0.55               | 30                | μs    |

| t <sub>BL</sub>  | Byte Load Window                         | 100                |                   | μs    |

| t <sub>WC</sub>  | Write Cycle Time                         |                    | 10 <sup>(3)</sup> | ms    |

| t <sub>DB</sub>  | Time to Device Busy                      | 120                |                   | ns    |

| t <sub>DW</sub>  | Write Start Time                         | 150 <sup>(4)</sup> |                   | ns    |

| t <sub>RP</sub>  | Reset Protect Time                       | 100                |                   | μs    |

| t <sub>RES</sub> | Reset High Time <sup>(5)</sup>           | 1                  |                   | μs    |

# **READ TIMING WAVEFORM**

Austin Semiconductor, Inc.

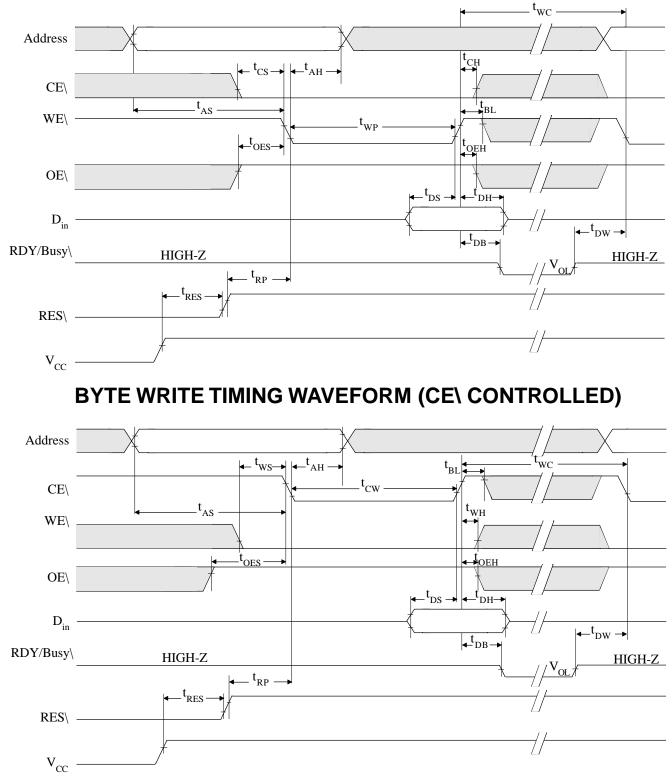

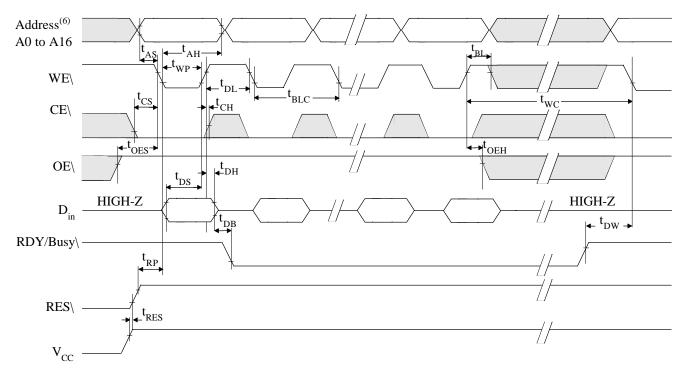

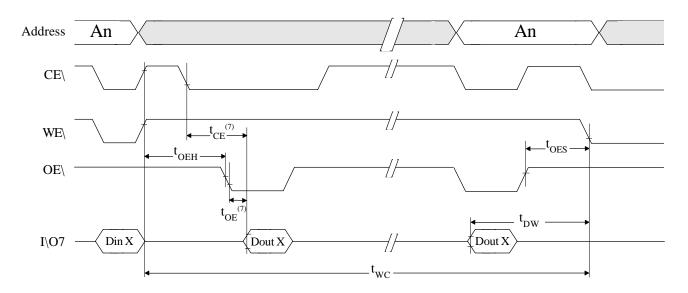

# BYTE WRITE TIMING WAVEFORM (WE\ CONTROLLED)

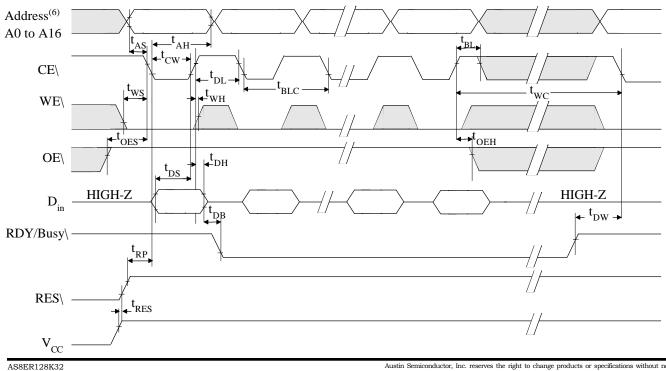

# PAGE WRITE TIMING WAVEFORM (WE\ CONTROLLED)

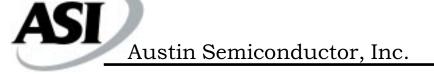

PAGE WRITE TIMING WAVEFORM (CE\ CONTROLLED)

## DATA POLLING TIMING WAVEFORM

### NOTES:

- 1.  $t_{DF}$  and  $t_{DFR}$  are defined as the time at which the outputs achieve the open circuit conditions and are no longer driven. 2. Use this device in longer cycle than this value.

3. two must be longer than this value unless polling techniques or RDY/Busy\ are used. This device automatically completes the internal write operation within this value.

- 4. Next read or write operation can be initiated after t<sub>DW</sub> if polling techniques or RDY/Busy\ are used.

- 5. This parameter is sampled and not 100% tested.

- 6. A7 to A16 are page addresses and must be same within the page write operation.

- 7. See AC read characteristics.

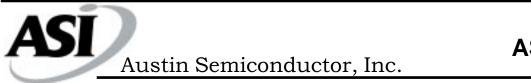

### **TOGGLE BIT**

This device provides another function to determine the internal programming cycle. If the EEPROM is set to read mode during the internal programming cycle, I/O6 will charge from "1" to "0" (toggling) for each read. When the internal programming cycle is finished, toggling of I/O6 will stop and the device can be accessible for next read or program.

### NOTES:

- 1) I/O6 beginning state is "1".

- 2) I/O6 ending state will vary.

- 3) See AC read characteristics.

- 4) Any locations can be used, but the address must be fixed.

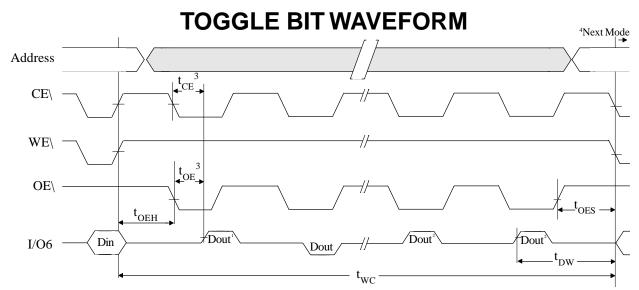

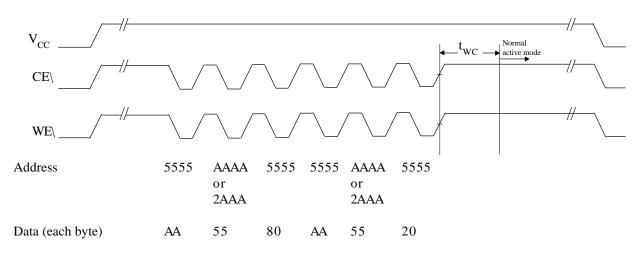

### SOFTWARE DATA PROTECTION TIMING WAVEFORM (In protection mode)

\* During this write cycle, data is physically written to the address provided.

### SOFTWARE DATA PROTECTION TIMING WAVEFORM (In non-protection mode)

### FUNCTIONAL DESCRIPTION

#### Automatic Page Write

Page-mode write feature allows 1 to 128 bytes of data to be written into the EEPROM in a single write cycle. Following the initial byte cycle, an additional 1 to 128 bytes can be written in the same manner. Each additional byte load cycle must be started within 30µs from the preceding falling edge of WE\ or CE\. When CE\ or WE\ is kept high for 100µs after data input, the EEPROM enters write mode automatically and the input data are written into the EEPROM.

### DATA\ Polling

DATA\ polling allows the status of the EEPROM to be determined. If EEPROM is set to read mode during the write cycle, an inversion of the last byte of data to be loaded outputs from I/O's 7, 15, 23, and 31 to indicate that the EEPROM is performing a write operation.

#### **RDY/Busy\ Signal**

RDY/Busy\ signal also allows status of the EEPROM to be determined. The RDY/Busy\ signal has high impedance except in write cycle and is lowered to  $V_{OL}$  after the first write signal. At the end of write cycle, the RDY/Busy\ signal changes state to high impedance.

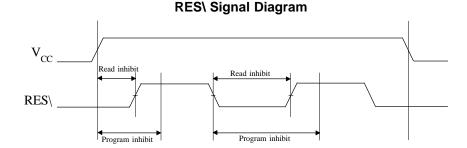

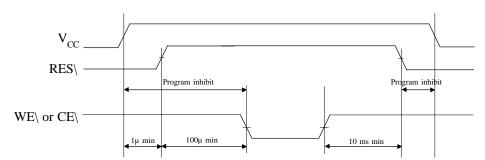

### **RES**\ Signal

When RES\ is low, the EEPROM cannot be read or programmed. Therefore, data can be protected by keeping RES\ low when  $V_{CC}$  is switched. RES\ should be high during read and programming because it doesn't provide a latch function. See timing diagram below.

### WE\, CE\ Pin Operation

During a write cycle, address are latched by the falling edge of WE\ or CE\, and data is latched by the rising edge of WE\ or CE\.

### Write/Erase Endurance and Data Retention Time

The endurance is  $10^4$  cycles in case of the page programming and  $10^3$  cycles in case of the byte programming (1% cumulative failure rate). The data retention time is more than 10 years when a device is page-programmed less than  $10^4$  cycles.

### RDY/Busy\SIGNAL

RDY/Busy\ signal also allows status of the EEPROM to be determined. The RDY/Busy\ signal has high impedance except in write cycle and is lowered to  $V_{OL}$  after the first write signal. At the end of the write cycle, the RDY/Busy\ signal changes state to high impedance. This allows many 58C1001 devices RDY/Busy\ signal lines to be wired-OR together.

### **PROGRAMMING/ERASE**

The 58C1001 does **NOT** employ a BULK-erase function. The memory cells can be programmed '0' or '1'. A write cycle performs the function of erase & write on every cycle with the erase being transparent to the user. The internal erase data state is considered to be '1'. To program the memory array with background of ALL 0's or All 1's, the user would program this data using the page mode write operation to program all 1024 128-byte pages.

### **Data Protection**

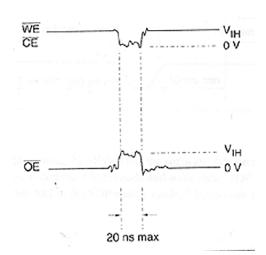

# 1. Data Protection against Noise on Control Pins (CE\, OE\, WE\) During Operation

During readout or standby, noise on the control pins may act as a trigger and turn the EEPROM to programming mode by mistake. To prevent this phenomenon, this device has a noise cancellation function that cuts noise if its width is 20ns or less in program mode.

EEPROM

AS8ER128K32

Be careful not to allow noise of a width more than 20ns on the control pins. See Diagram 1 below.

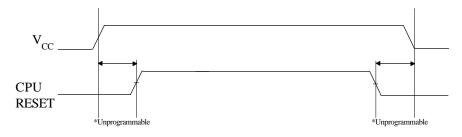

### 2. Data Protection at $V_{CC}$ On/Off

When  $V_{CC}$  is turned on or off, noise on the control pins generated by external circuits (CPU, etc.) may act as a trigger and turn the EEPROM to program mode by mistake. To prevent this unintentional programming, the EEPROM must be kept in an unprogrammable state while the CPR is in an unstable state.

NOTE: The EEPROM should be kept in unprogrammable state during  $V_{CC}$  on/off by using CPU RE-SET signal. See the timing diagram below.

DIAGRAM 1

### DATA PROTECTION AT V<sub>CC</sub> ON/OFF

#### Data Protection Cont.

a. Protection by RES

The unprogrammable state can be realized by the CPU's reset signal inputs directly to the EEPROM's RES pin. RES should be kept  $V_{SS}$  level during  $V_{CC}$  on/off.

The EEPROM brakes off programming operation when RES becomes low, programming operation doesn't finish correctly in case that RES falls low during programming operation. RES should be kept high for 10ms after the last data inputs. See the timing diagram below.

#### 3. Software data protection

To prevent unintentional programming, this device has the software data protection (SDP) mode. The SDP is enabled by inputting the 3 bytes code and write data in Chart 1. SDP is not enabled if only the 3 bytes code is input. To program data in the SDP enable mode, 3 bytes code must be input before write data. This 4th cycle during write is required to initiate the SDP and physically writes the address and data. While in SDP the entire array is protected in which writes can only occur if the exact SDP sequence is re-executed or the unprotect sequence is executed.

The SDP is disabled by inputting the 6 bytes code in Chart 2. Note that, if data is input in the SDP disable cycle, data can not be written.

The software data protection is not enabled at the shipment.

NOTE: These are some differences between ASI's and other company's for enable/disable sequence of software data protection. If these are any questions, please contact ASI.

### **PROTECTION BY RES\**

| CHART 1       |                                |  |  |  |  |

|---------------|--------------------------------|--|--|--|--|

| Address       | Data<br>(each Byte)            |  |  |  |  |

| 5555<br>↓     | AA<br>L                        |  |  |  |  |

| AAAA or 2AAA  | 55                             |  |  |  |  |

| 5555<br>      | A0<br>L                        |  |  |  |  |

| Write Address | Write Data } Normal data input |  |  |  |  |

|               |                                |  |  |  |  |

| CHART 2      |              |  |  |  |

|--------------|--------------|--|--|--|

| Address      | Data         |  |  |  |

|              | (each Byte)  |  |  |  |

| 5555         | AA           |  |  |  |

| <b>V</b>     | $\checkmark$ |  |  |  |

| AAAA or 2AAA | 55           |  |  |  |

| . ↓          | $\checkmark$ |  |  |  |

| 5555         | 80           |  |  |  |

| $\downarrow$ | $\downarrow$ |  |  |  |

| 5555         | ĂĂ           |  |  |  |

| $\downarrow$ | $\downarrow$ |  |  |  |

| AAAA or 2AAA | 55           |  |  |  |

| $\downarrow$ | Ļ            |  |  |  |

| 5555         | 20           |  |  |  |

|              | _ 3          |  |  |  |

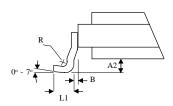

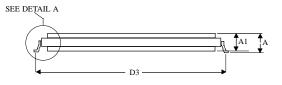

# **MECHANICAL DEFINITIONS\***

ASI Case #703 (Package Designator Q)

DETAIL A

|        | ASI PACKAGE SPECIFICATIONS |       |  |

|--------|----------------------------|-------|--|

| SYMBOL | MIN                        | MAX   |  |

| A      | 0.123                      | 0.200 |  |

| A1     | 0.118                      | 0.186 |  |

| A2     | 0.000                      | 0.020 |  |

| b      | 0.013                      | 0.017 |  |

| В      | 0.010 REF                  |       |  |

| D      | 0.800 BSC                  |       |  |

| D1     | 0.870                      | 0.890 |  |

| D2     | 0.980                      | 1.000 |  |

| D3     | 0.936                      | 0.956 |  |

| е      | 0.050 BSC                  |       |  |

| R      | 0.005                      |       |  |

| L1     | 0.035                      | 0.045 |  |

#### \*All measurements are in inches.

## **ORDERING INFORMATION**

**EXAMPLE:** AS8ER128K32Q-15/XT

| Device Number | Package<br>Type | Speed<br>ns | Process |

|---------------|-----------------|-------------|---------|

| AS8ER128K32   | Q               | -15         | /*      |

### **\*AVAILABLE PROCESSES**

| IT = Industrial Temperature Range | $-40^{\circ}$ C to $+85^{\circ}$ C |

|-----------------------------------|------------------------------------|

| XT = Extended Temperature Range   | -55°C to +125°C                    |